When executed in the architecture register, the two CMP instructions are register-independent, so they can be executed at the same time, but the cpsr register has only one, so the two instructions can not be executed simultaneously. The result of the CMP instruction (*4) updates the NZCV flag in the cpsr register. Since the same registers are not used, the STR and LDR instructions can be executed simultaneously. The Cortex-A9 processor automatically replaces the physical registers and renames the STR instruction r0=p0/r1=p1 and the LDR instruction r0=p2/r2=p3. Because architectural registers use the same register (r0) for store and load data for different addresses, the LDR instruction cannot be executed until the STR instruction is completed.

This section describes the operation of register renaming when successive STR (*2) and LDR (*3) instructions are executed in succession. The virtual flags (flg0-flg7) have copies of the cpsr flags NZCV, GE and Q bits.Ĭoding and debugging uses architecture registers and does not allow the use of physical registers. Physical registers (p0-p55) and virtual flags (flg0- flg7) that are physically implemented in the processor.Architecture registers used by the software (r-0r15, cpsr).The Cortex-A9 processor has two classes of registers. You can see that it is not easy to increase the “Rd” field, since all the other bits are used.Īs a solution to this problem, the Cortex-A9 has a “register renaming” function.Īrchitecture Registers and Physical Registers In the “MOV.W, #” instruction, the “Rd” field indicates the register number in 4 bits. Increasing the number of registers in a processor architecture means changing the instruction set architecture, which cannot be easily changed. When developing a program, the function call is “ It is specified in AAPCS (Procedure Call Standard for Arm Architecture)” and not all registers are available. However, not all processing can be done between registers. In order to increase instruction execution efficiency, programs can be executed faster by accessing as little data to memory as possible and performing processing between registers.

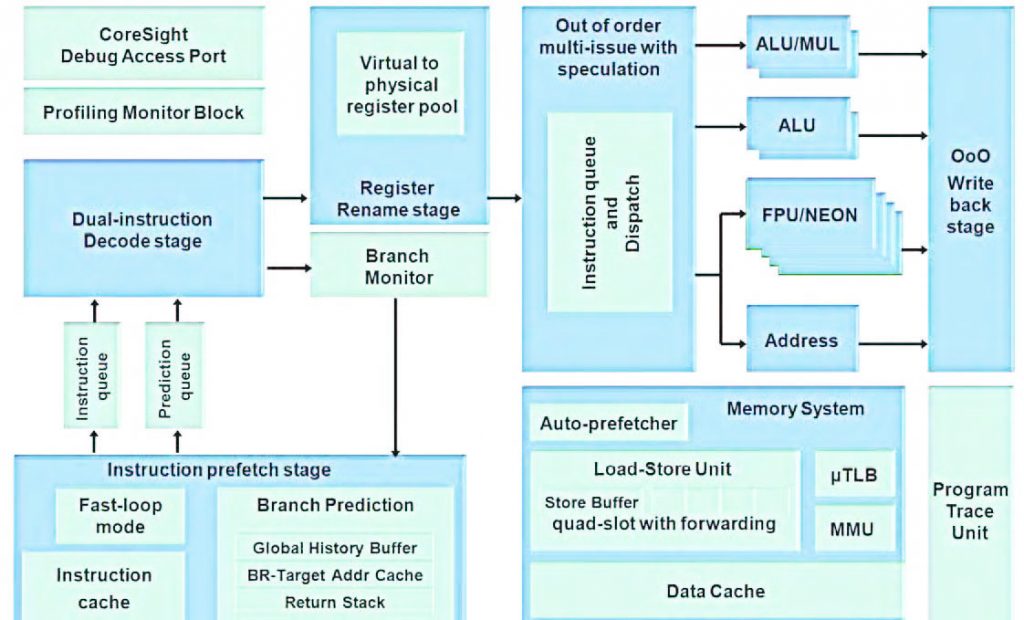

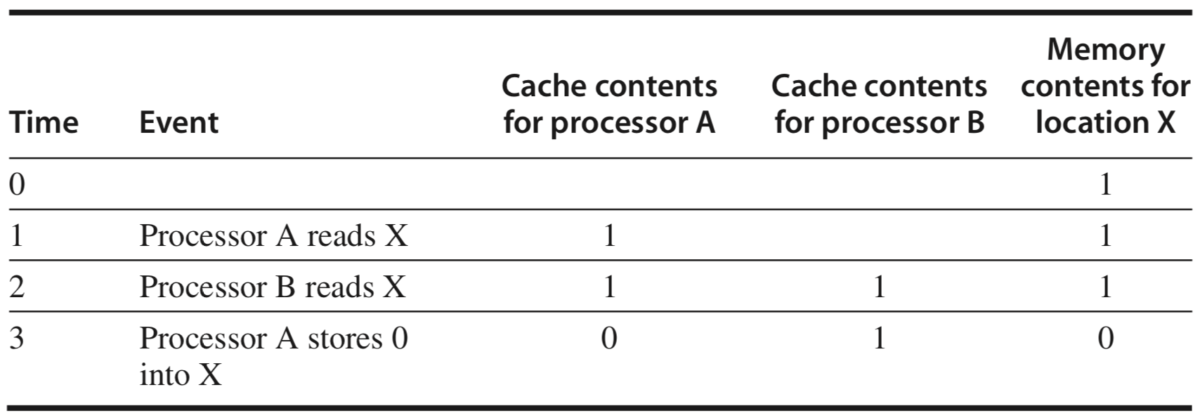

This section describes the unique features of the Cortex-A9 processor. (*1) What is the MESI protocol? A cache coherency and memory consistency protocol that synchronizes memory and cache in multiprocessor systems and is widely used in write-back caches. All CPUs in the cluster can reference it. Private Timers and Watchdog TimersĮach processor has a private timer and a watchdog timer. Routing and prioritization of inter-processor communication and system interrupts. Manages coherency of L1 data cache between processors during SMP operation, using a modified version of the MESI protocol(*1) General-purpose Interrupt Controller The Cortex-A9 MPCore has the following features Snoop Control Unit The Cortex-A9 MPCore can support multi-core configurations of up to four processors, either asymmetric multiprocessing (AMP) or symmetric multiprocessing (SMP). Increased security through TrustZone extensions.Variable length multiple issue pipeline.Program flow trace (PTM: Program Trace Macrocell) and performance monitoring units on the Cortex-A9 can be used to verify program behavior. Optional VFP-v3-D16 or NEON media processing engines and TrustZone security extensions can be included to increase system performance and reliability. The Cortex-A9 processor is an Armv7-A architecture and can be configured in a multi-core configuration from one to four cores. Overview of the Cortex-A9 processor control method.

0 Comments

Leave a Reply. |

AuthorWrite something about yourself. No need to be fancy, just an overview. ArchivesCategories |

RSS Feed

RSS Feed